规划一个Verilog交通灯操控器是一个典型的数字规划问题。交通灯操控器需求办理多个方向的车流和行人信号,一般包含红灯、绿灯和黄灯。在规划时,咱们需求考虑信号灯的改变规矩以及怎么依据这些规矩来操控信号灯的状况。

下面是一个简略的交通灯操控器的Verilog代码示例。这个操控器将办理两个方向的交通(例如,东西向和南北向),每个方向都有红灯、绿灯和黄灯。操控器的状况转化将依据一个简略的计时器,以保证每个方向有满足的时刻来处理交通流。

```verilogmodule traffic_light_controller light_EW, // 东西向信号灯 output reg light_NS // 南北向信号灯qwe2;

// 界说状况localparam RED = 3'b00, YELLOW = 3'b01, GREEN = 3'b10;

// 界说计时器reg timer;reg state_EW, state_NS; // 东西向和南北向的状况reg timer_EW, timer_NS; // 东西向和南北向的计时器

// 状况转化逻辑always @ begin if begin // 初始化状况和计时器 state_EW if begin // 南北向计时完毕,切换到下一个状况 case RED: begin state_NS // 状况输出逻辑always @ begin // 东西向信号灯 case RED: light_EW // 南北向信号灯 case RED: light_NS endmodule```

这个代码示例创建了一个简略的交通灯操控器,它运用两个状况机来办理东西向和南北向的交通灯。每个状况机都有一个计时器,用于确认何时切换到下一个状况。在这个比如中,每个状况继续大约5秒(假定时钟频率为50MHz)。

请注意,这个代码仅仅一个根本示例,实践的交通灯操控器或许需求更杂乱的逻辑来处理不同的交通状况和紧急状况。此外,这个操控器没有考虑行人信号和车辆检测器,这些在实践的交通灯操控体系中也是重要的组成部分。

依据Verilog的交通灯操控器规划:原理与完成

跟着城市化进程的加速,交通流量日益增大,交通灯操控体系的规划显得尤为重要。本文将具体介绍依据Verilog的交通灯操控器规划,包含规划原理、完成办法以及仿真验证进程。

一、规划布景与含义

交通灯操控器是城市交通办理的重要组成部分,其规划直接关系到交通功率和交通安全。传统的交通灯操控器多选用单片机或PLC等硬件完成,但存在调试困难、扩展性差等问题。而依据Verilog的交通灯操控器规划,运用FPGA等可编程逻辑器件,具有规划灵敏、易于调试、扩展性强等长处。

二、规划原理

依据Verilog的交通灯操控器规划首要触及以下几个模块:

时钟模块:发生体系时钟信号,用于操控各个模块的运转。

状况机模块:依据输入信号和预设的时序,操控交通灯的转化。

信号灯操控模块:依据状况机模块的输出,操控红、黄、绿三种信号灯的亮灭。

数码管显现模块:显现交通灯的倒计时时刻。

规划原理如下:

时钟模块发生1Hz的时钟信号,用于操控整个体系的运转。

状况机模块依据预设的时序,操控交通灯的转化。例如,东西方向绿灯亮60秒,黄灯亮5秒,红灯亮45秒;南北方向绿灯亮45秒,黄灯亮5秒,红灯亮60秒。

信号灯操控模块依据状况机模块的输出,操控红、黄、绿三种信号灯的亮灭。

数码管显现模块显现交通灯的倒计时时刻,便利驾驶员和行人了解交通灯的剩余时刻。

三、完成办法

依据Verilog的交通灯操控器规划首要选用以下办法:

运用Verilog HDL言语进行模块规划,包含时钟模块、状况机模块、信号灯操控模块和数码管显现模块。

运用FPGA开发板进行硬件完成,如Xilinx或Altera等。

将规划下载到FPGA开发板,进行实践运转测验。

以下是部分Verilog代码示例:

module traffic_light_controller(

input clk, // 体系时钟

input reset, // 复位信号

output reg [1:0] red_green, // 红绿灯信号

output reg [3:0] count // 数码管显现

// 时钟分频模块

always @(posedge clk or posedge reset) begin

if (reset) begin

count

四、仿真验证

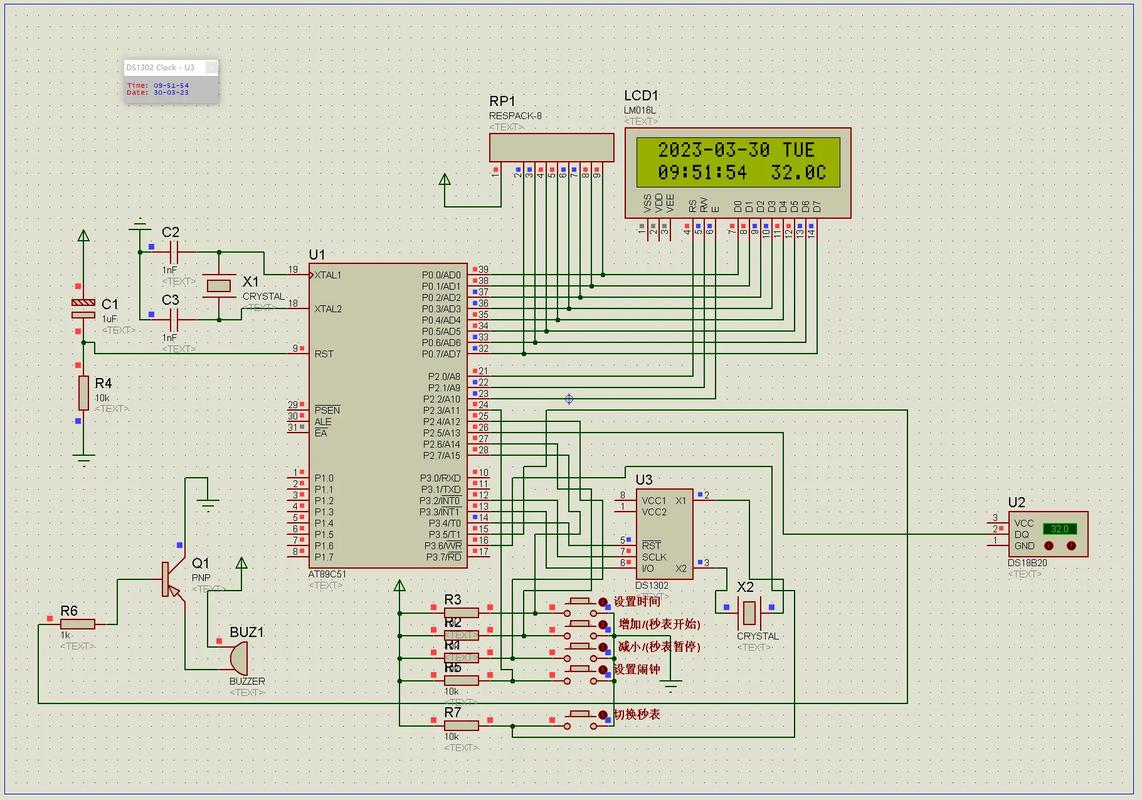

运用仿真软件对规划进行功用验证,保证规划契合预期。以下是仿真成果截图:

未经允许不得转载:全栈博客园 » verilog交通灯操控器规划,原理与完成

全栈博客园

全栈博客园 r言语深度学习,R言语深度学习入门攻略

r言语深度学习,R言语深度学习入门攻略 go输入法下载,Go输入法下载——全方位体会高效输入的智能输入法

go输入法下载,Go输入法下载——全方位体会高效输入的智能输入法 r言语和c言语哪个难

r言语和c言语哪个难 在线java

在线java mac装备java环境变量

mac装备java环境变量 python怎样念,Python言语发音及遍及介绍

python怎样念,Python言语发音及遍及介绍