Verilog是一种硬件描绘言语,用于数字电路的规划和仿真。它答应规划者以文本方式描绘电路的行为和结构,然后运用仿真东西来验证电路的功用。Verilog的语法类似于C言语,因而关于了解C言语的工程师来说,学习Verilog会相对简略一些。

Verilog的主要特点包括:

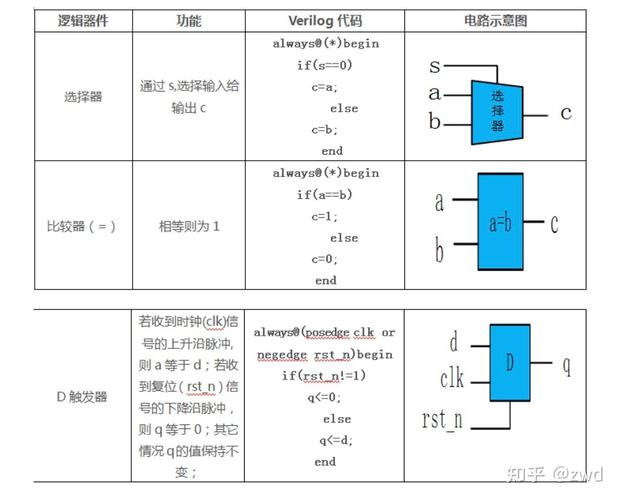

模块化规划: Verilog答应规划者将电路分解成多个模块,每个模块能够独立规划、仿真和测验。 行为描绘: Verilog能够运用进程句子来描绘电路的行为,例如ifelse句子、case句子和循环句子。 结构描绘: Verilog也能够运用结构句子来描绘电路的结构,例如assign句子、wire声明和module声明。 仿真: Verilog仿真东西能够模仿电路在不同输入条件下的行为,协助规划者验证电路的功用。 归纳: Verilog归纳东西能够将Verilog代码转换为实践的硬件电路,例如FPGA或ASIC。

学习Verilog的途径:

Verilog入门:怎么阅览和了解Verilog代码

Verilog是一种硬件描绘言语(HDL),用于规划和描绘数字电路。它广泛应用于集成电路规划、FPGA编程和ASIC开发等范畴。关于初学者来说,阅览和了解Verilog代码可能是一项应战。本文将介绍怎么开端阅览和了解Verilog代码。

Verilog是一种高档言语,它答应工程师运用类似于C或C 的语法来描绘电路的行为和结构。Verilog代码一般用于创立模仿和仿真模型,以及用于实践硬件的配置文件。

模块(Module):Verilog代码的根本单元,类似于C言语中的函数。

实例(Instance):模块的实例化,类似于C言语中的目标。

信号(Signal):用于在模块之间传递数据的线。

赋值句子:用于设置信号值的句子,如`assign`。

always块:用于描绘时序逻辑的块。

initial块:用于描绘初始化逻辑的块。

了解模块结构

辨认信号和端口

剖析always和initial块

了解赋值句子和逻辑表达式

查看时序和同步问题

参阅文档和示例

每个Verilog模块都由一个模块界说开端,一般包括模块名、端口列表和模块体。以下是一个简略的模块示例:

module adder(input [3:0] a, input [3:0] b, output [4:0] sum);

assign sum = a b;

endmodule

在这个比如中,`adder`是一个模块,它有两个4位的输入信号`a`和`b`,以及一个5位的输出信号`sum`。

信号是Verilog中的数据载体,而端口是模块与外部国际交互的接口。在模块界说中,端口被声明为输入、输出或双向类型。以下是一个包括端口的模块示例:

module counter(input clk, input reset, output [3:0] count);

reg [3:0] current_count;

wire [3:0] next_count;

always @(posedge clk or posedge reset) begin

if (reset)

current_count

在这个比如中,`clk`和`reset`是输入端口,而`count`是输出端口。`current_count`和`next_count`是内部信号。

Verilog中的`always`块用于描绘时序逻辑,而`initial`块用于描绘初始化逻辑。以下是一个`always`块的示例:

always @(posedge clk or posedge reset) begin

if (reset)

current_count

这个`always`块在每个时钟上升沿或复位信号上升沿时履行。假如复位信号为高,则`current_count`被重置为0;不然,它被更新为`next_count`的值。

非堵塞赋值(

堵塞赋值(=):用于时序逻辑,如`current_count

未经允许不得转载:全栈博客园 » verilog怎样读,怎么阅览和了解Verilog代码

全栈博客园

全栈博客园 123go

123go php怎样装置,PHP环境建立与装置攻略

php怎样装置,PHP环境建立与装置攻略 pascal命名法,什么是Pascal命名法?

pascal命名法,什么是Pascal命名法? php一句话木马

php一句话木马 聚类剖析r言语,办法、实例与技巧

聚类剖析r言语,办法、实例与技巧 java下载我的国际,轻松敞开沙盒冒险之旅

java下载我的国际,轻松敞开沙盒冒险之旅 r言语hist,R言语中的直方图制作——hist函数详解

r言语hist,R言语中的直方图制作——hist函数详解