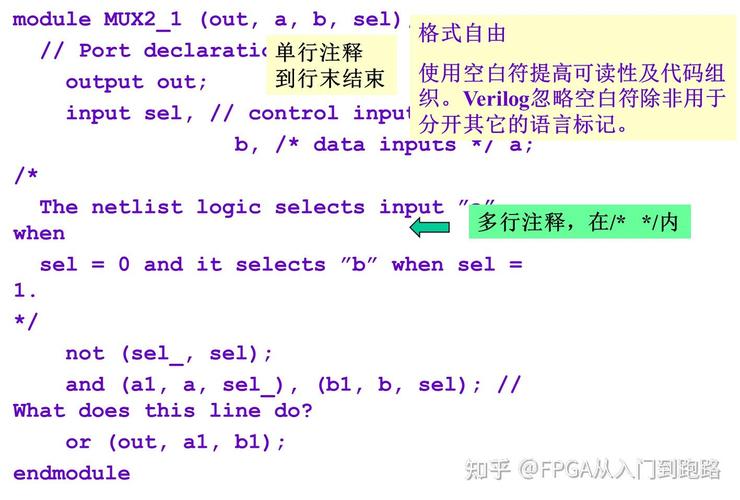

1. 模块(Module): 每个Verilog文件包括一个或多个模块,模块是Verilog代码的根本构建块。 模块界说了电路的功用和结构。 模块声明以要害字 `module` 开端,以 `endmodule` 完毕。

2. 模块端口(Ports): 模块端口是模块与其他模块或外部国际交互的接口。 端口可所以输入(input)、输出(output)或双向(inout)。

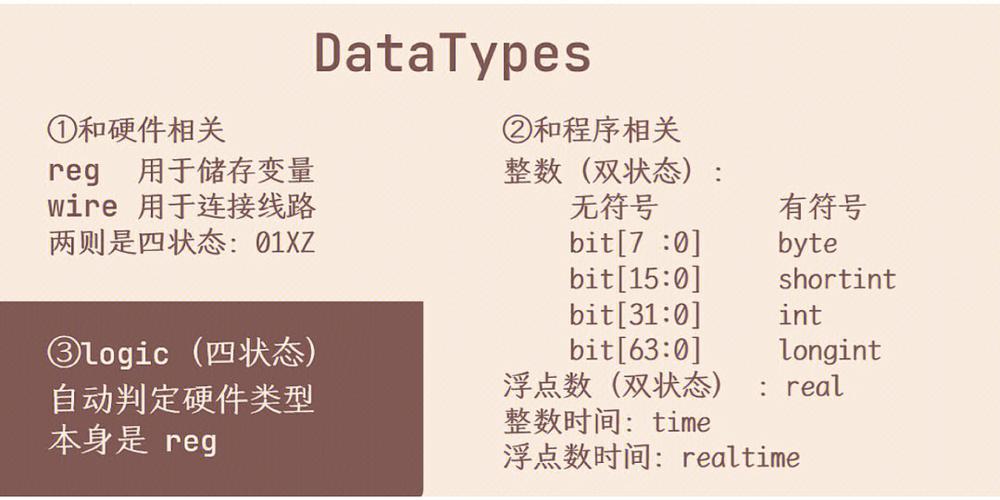

3. 数据类型(Data Types): Verilog支撑多种数据类型,包括线(wire)、寄存器(reg)、整数(integer)等。 线(wire)一般用于衔接模块端口,而寄存器(reg)用于存储值。

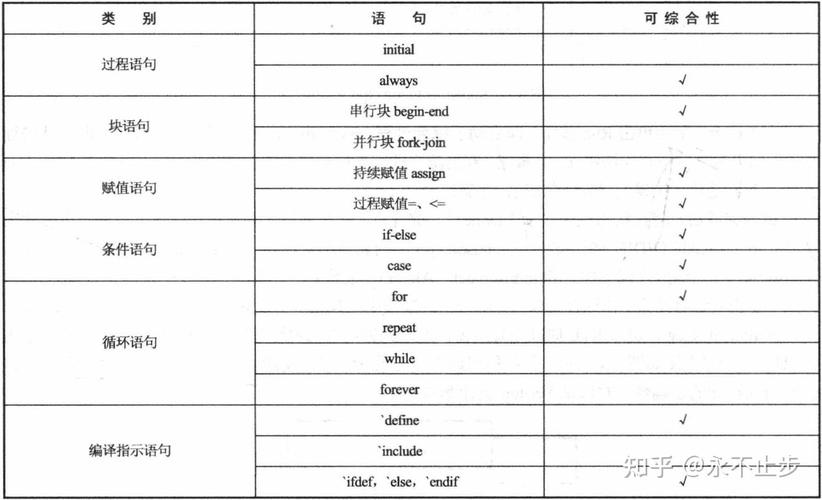

4. 信号赋值(Signal Assignment): Verilog中的信号赋值能够运用堵塞赋值(`=`)或非堵塞赋值(`5. 时序操控(Timing Control): Verilog运用时刻操控句子来指定信号何时改动。 常见的时刻操控句子包括 ``(推迟)、`@`(事情)和 `wait`。

6. 条件句子(Conditional Statements): Verilog支撑条件句子,如 `ifelse` 和 `case`。 这些句子用于依据条件履行不同的操作。

7. 循环句子(Loop Statements): Verilog支撑循环句子,如 `for`、`while` 和 `forever`。 这些句子用于重复履行一组句子。

8. 使命和函数(Tasks and Functions): Verilog支撑使命和函数,用于封装可重用的代码。 使命和函数能够承受参数并返回值。

9. 体系使命和函数(System Tasks and Functions): Verilog供给了一系列体系使命和函数,用于仿真操控和调试。 常见的体系使命和函数包括 `$display`、`$monitor` 和 `$finish`。

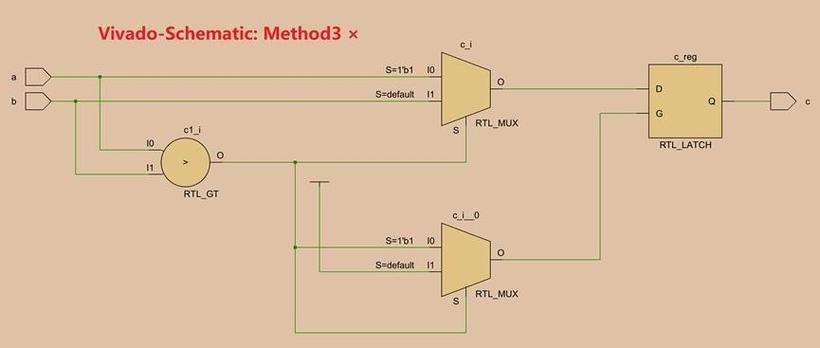

10. 仿真和归纳(Simulation and Synthesis): Verilog代码能够用于仿真和归纳。 仿真用于验证电路的功用,而归纳用于将Verilog代码转换为硬件。

以上是Verilog的一些根本语法和概念,但Verilog是一种十分强壮的言语,还有许多其他特性和功用。要深化了解Verilog,主张参阅相关的教程和文档。

Verilog语法简介

Verilog是一种硬件描绘言语(HDL),用于规划和描绘数字电路。它广泛应用于集成电路规划、FPGA编程和ASIC开发等范畴。本文将扼要介绍Verilog的语法结构,协助读者快速了解这一编程言语的根本要素。

Verilog要害字

module:界说一个模块

endmodule:模块完毕

reg:界说寄存器

wire:界说线网

input:界说输入端口

output:界说输出端口

assign:赋值句子

initial:初始化块

always:总是块

Verilog数据类型

integer:整数类型

real:实数类型

time:时刻类型

bit:位类型

logic:逻辑类型

std_logic:规范逻辑类型

Verilog模块结构

Verilog模块是Verilog程序的根本单元,用于描绘电路的功用。一个模块一般包括以下部分:

模块界说:运用`module`要害字界说模块,并指定模块名

端口列表:界说模块的输入和输出端口

内部信号界说:界说模块内部的信号

模块体:包括模块的逻辑描绘,如always块和initial块

模块完毕:运用`endmodule`要害字完毕模块界说

Verilogalways块

always块是Verilog中用于描绘时序逻辑的要害结构。它表明一个进程,该进程在满意特定条件时履行。以下是一个简略的always块示例:

always @(posedge clk) begin

if (reset)

reg_value

在这个比如中,always块在时钟信号上升沿触发,依据reset信号和data_in信号来更新reg_value寄存器的值。

Veriloginitial块

initial块是Verilog中用于描绘初始化逻辑的要害结构。它表明一个进程,该进程在仿真开端时履行一次。以下是一个简略的initial块示例:

initial begin

$monitor(\

未经允许不得转载:全栈博客园 » verilog语法,Verilog语法简介

全栈博客园

全栈博客园 字典python, 什么是Python字典?

字典python, 什么是Python字典? php 快速排序, 快速排序原理

php 快速排序, 快速排序原理 python图画处理

python图画处理 r言语par,绘图参数的强壮东西

r言语par,绘图参数的强壮东西 编程软件python,助力开发者高效编程的利器

编程软件python,助力开发者高效编程的利器 jav go,深入探讨Java与Go言语的差异与运用场景

jav go,深入探讨Java与Go言语的差异与运用场景 go谷歌装置器官网

go谷歌装置器官网